RTL级设计的评判标准

时序性能、所占面积、可测试性、可重用性、功耗、时钟域的分配、复位信号设计、是否与所用EDA工具匹配

指导原则:面积与速度互换 、乒乓操作、 流水线设计

面积与速度互换

**面积:**一个设计所消耗的目标器件的硬件资源数量或者ASIC芯片的面积

**速度:**设计在芯片上稳定运行时所能够达到的最高频率,这个频率是有设计的时序状况决定

时钟周期、PAD to PAD Time、Clock Setup Time、Clock Hold Time、Clock-to-Output Delay

面积与速度的平衡互换原则

**设计面积小与运行频率高是对立统一的矛盾体。**科学的设计目标是:

-

在满足设计时序要去(包含对设计最高频率的要求)的前提下,占用最小的芯片面积;

-

在所规定的面积下,使设计的时序余量更大,频率更高

设计如果时序余量较大,所能跑的频率远远高于设计要求:

- 通过功能模块复用减少整个设计所消耗的芯片面积,用速度的优势对换面积的节约。

设计的时序要求很高,普通方法达不到设计频率:

-

可以通过将数据流串并转换;

-

并行复制多个操作模块;

-

对整个设计采取乒乓操作和串并转换的细想进行处理;

-

在芯片输出模块处,在对数进行“并串转换”

乒乓操作

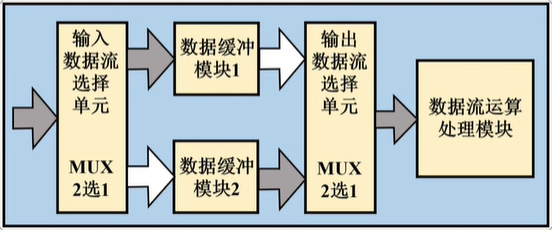

“乒乓操作”是一个常常应用于数据流控制的处理技巧

数据缓冲模块可以为常用的存储的单元:双口RAM 单口RAM FIFO

第1个缓冲周期,将输入数据缓冲到模块1;

第2个缓冲周期,通过切换输入数据流选择单元,将输入数据缓冲到模块2。同时将数据缓冲模块1缓冲的数据,通过输出数据流选择单元进行的选择送到数据流运算模块进行运算处理;

第3个缓冲周期,通过输入数据流选择单元的再次切换,将输入数据缓冲到数据缓冲模块1.同时,将数据缓冲模块2缓冲的第2个周期的数据通过输出数据流选择单元的切换,送到数据流处理模块;

如此循环,完成数据的输入。

特点:

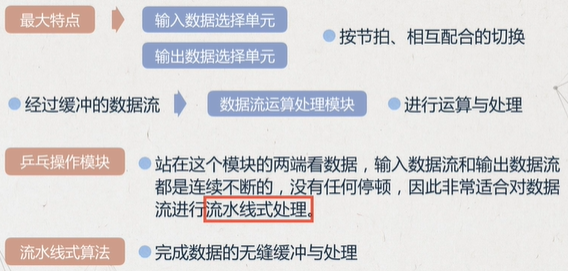

乒乓操作的最大特点是通过“输入数据选择单元”和“输出数据选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有停顿地送到“数据流运算处理模块”进行运算与处理。把乒乓操作模块当做一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理。所以乒乓操作常常应用于流水线式算法,完成数据的无缝缓冲与处理。

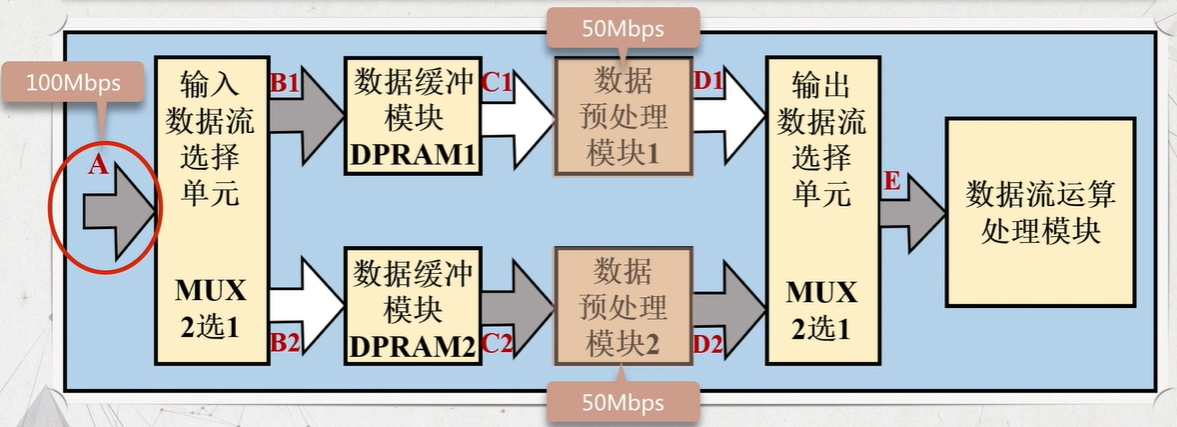

乒乓操作的第二个优点是可以节约缓冲区空间。另外,巧妙运用乒乓操作还可以达到用低速模块处理高速数据流的效果。如视频中实例展示,通过乒乓操作实现低速模块处理高速数据的实质是:通过DPRAM这种缓存单元实现了数据流的串并转换,并行用“数据预处理模块1”和“数据预处理模块2”处理分流的数据,是面积与速度互换原则的体现!

通过乒乓操作实现低速模块处理高速数据的实质如下图所示。

通过DPRAM这种缓存单元实现了数据流的串并转换,并行用“数据预处理模块1”和“数据预处理模块2”处理分流的数据,是面积与速度互换原则的体现。

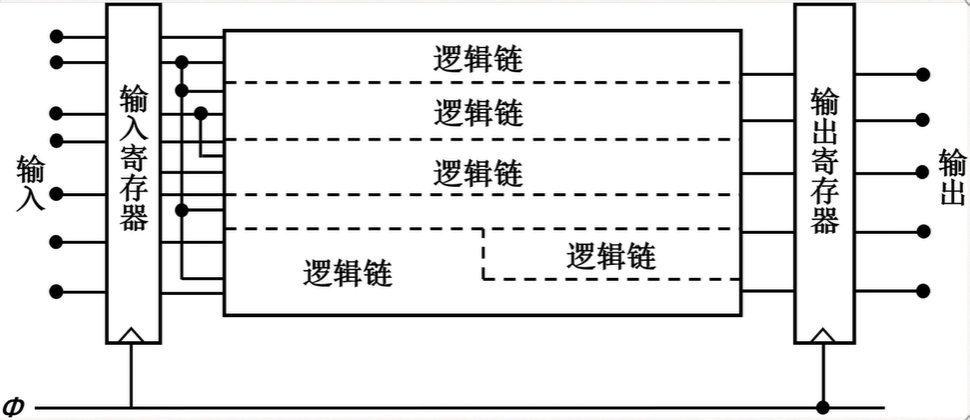

流水线

流水线的参数设计中,系统时钟取决于最慢的流水线级的延时。

最长的组合逻辑链 --> 最大的td值 --> 系统时钟频率上限 --> 系统速度上限

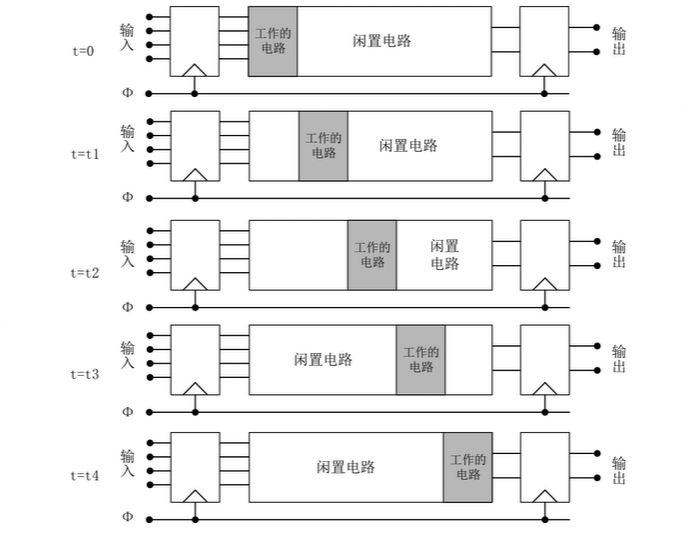

组合逻辑链的并行闲置:

组合逻辑链的串行闲置:

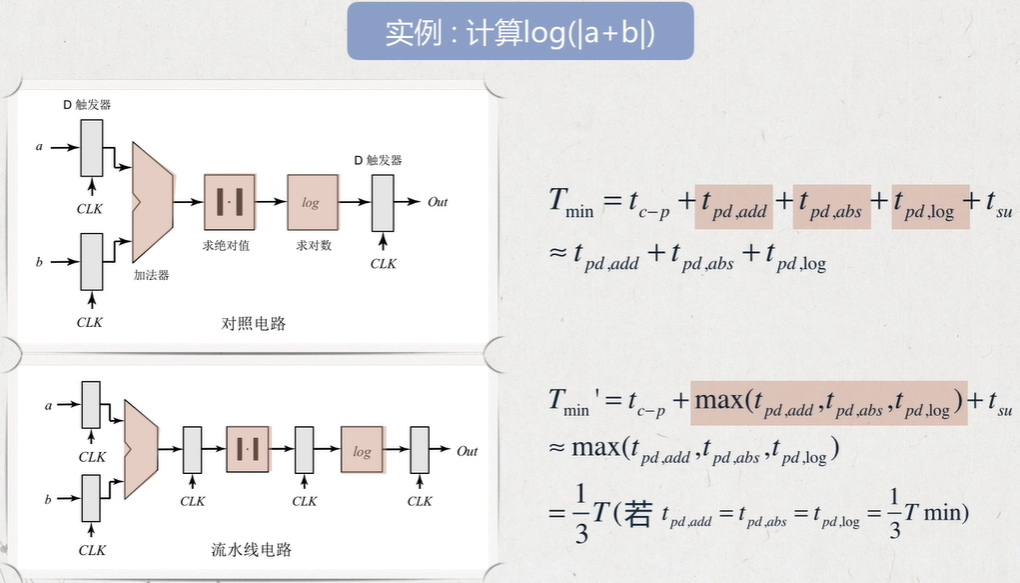

实例: 计算log(|a+b|)

组合逻辑的延时等于加法器,求绝对值,求对数的延时之和。如若插入两级寄存器之后,组合逻辑的延时等于三者绝对值的最大值,且每个时刻三部分都在运行。对比发现,流水线的工作方式可以充分提高电路运行的频率,理想情况下 ,本例中,运行频率可以提升至原来的三倍。

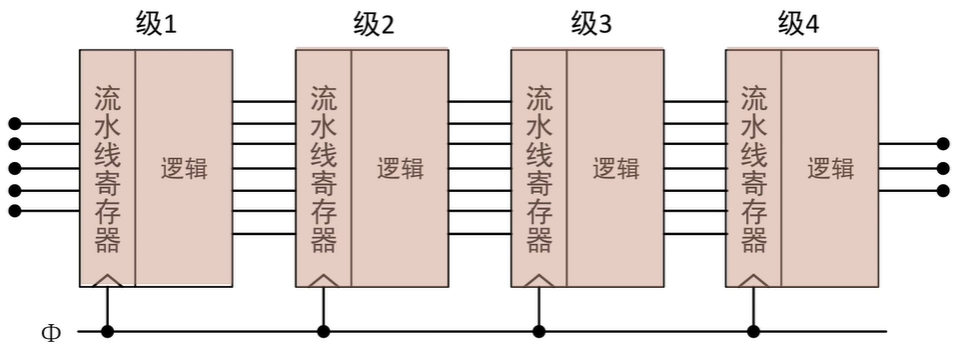

四级流水线结构

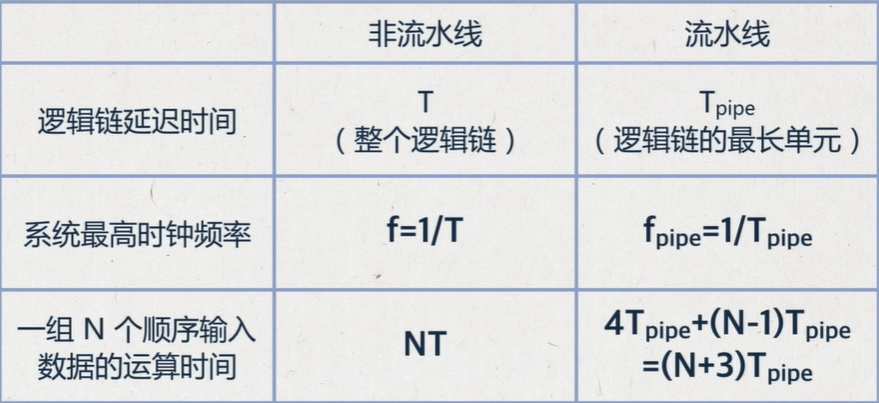

四级流水线比较

注:Tpipe<T(因流水线单元一定比非流水线单元短);4Tpipe>T(因流水线需要插入寄存器,寄存器有延迟)

特点:

通过插入寄存器,将长的串行逻辑链分成较小的部分。当系统运算是串行的时候,利用时钟控制,使运算依照顺序接续进行。在任何给定时刻,大部分电路都在工作。

好处:

每一部分延时较小–> 可使用更快的时钟

大部分电路同时进行运算–>可提高数据通过量

流水线参数设计

系统时钟取决于最慢的流水线级的延时

流水线时钟周期 Tpipe=max{T1,T2,… ,Tm}

第i级的时钟周期 Ti>tff + tsu + td,i + ts,i + 1

流水线分割点及级数的确定要考虑的因素包括:

- 单元延迟时间及时钟频率的大小决定了数据通过速率;

- 过多的级数不一定能产生最快的结果;

- 太多寄存器的插入会导致芯片面积增加,布线困难,时钟偏差增加。

参考:芯动力—硬件加速设计方法