“ 介绍SRAM基本存储单元,也分析了其设计和读写过程。”

01.最常见的SRAM cell,the full CMOS 6T 类型;

02.SRAM的读写过程;

03.执行读操作时最基本的电学稳定**特性,静态噪声裕量(SNM)

SRAM CELL

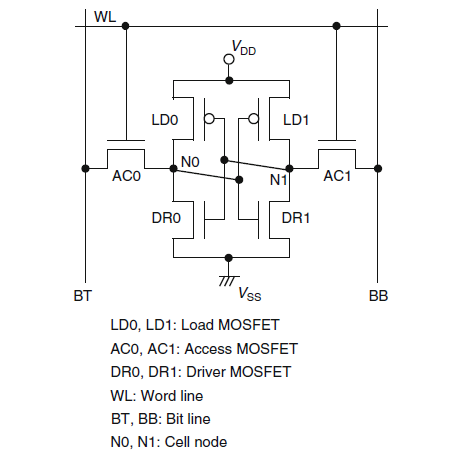

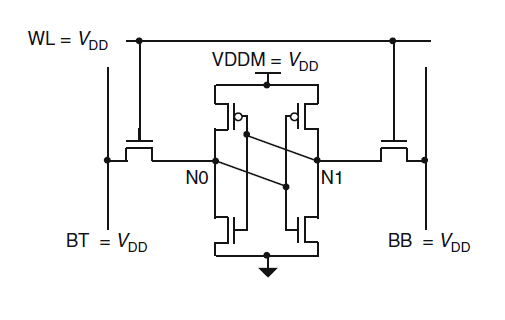

Fig.1 SRAM memory cell

SRAM cell由一个基本的触发器(flip-flop)单元构成,即两个交叉耦合(cross coupled)的反相器,于flip-flop的存储结点存储逻辑值“0”或“1”。

最常用的SRAM cell是全部由MOS管构成的6个晶体管构成的互补逻辑电路(full CMOS 6-transistor),就SOC(system-on-chip)设计而言,由于full CMOS 6-T使用的工艺为平面CMOS工艺,便于生成制造,故最常使用。

主要组成:

Fig. 2.1 SRAM cell with the full CMOS 6-transistor (6-T)

两个反相器(load MOSFET(LD0)-driver MOSFET(DR0), LD1-DR);

两个导通管(access MOSFET AC0, AC1)连接到一对bit line(BT,BB)上,同时,导通管的栅端(gate)连接到word line(WL);

为构成一个flip-flop,其中一个反相器的输入和输出端需要分别连接到另一个反相器的输出和输入端,也即是交叉耦合。

Basic Operation of SRAM Cell

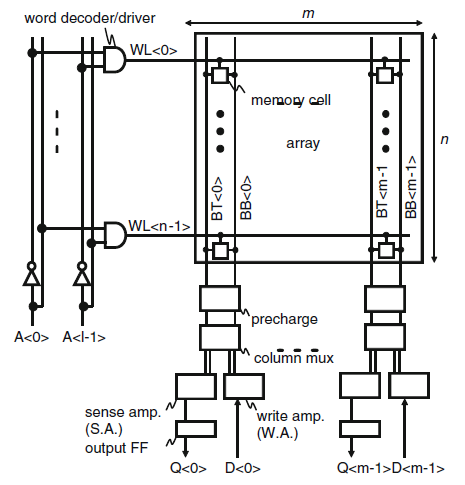

Memory的基本排列构造(array structure)如下图2.2所示,整个memory由nxm位memory cell组成。

Fig. 2.2 Basic full CMOS cell array structure

SRAM具体某一位cell的确定由横向和纵向上共同选中,横向上由**word line译码器(word decoder)根据地址数据选择一排word line(WL),纵向上bit line控制电路由预充电电路(precharge circuit),列选择器(Column multiplexer,MUX),灵敏放大器(sense amplifier ,SA),输出电路(output FF)和写放大器(write amplifier,SA)**构成。详细的电路结构在图2.3中。

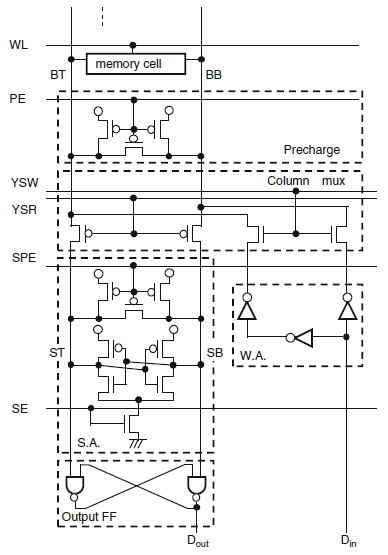

Fig. 2.3 Column control circuits consisting of precharge circuit, column multiplexer (mux),sense amplifier (SA), output FF, and write amplifier (WA)

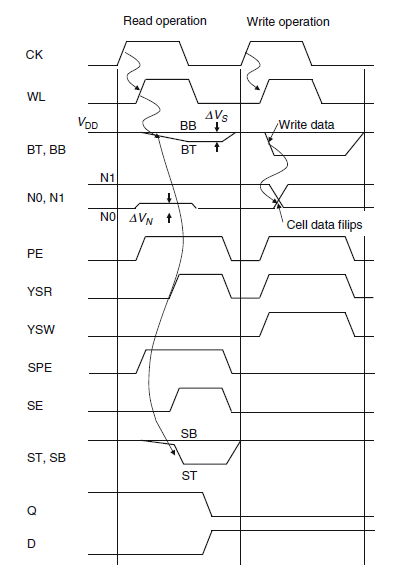

下面介绍SRAM读写操作,如图2.4所示电压波形。执行读操作需要给bit line先进行预充电(precharge),prechage电路平衡提升bit line的电位至VDD。****随后,word line置高,导通管打开,预先存储于存储节点的数据使cell产生一个小的电压变化(ΔVS)。

Fig. 2.4 Basic voltage waveform in read and write operation

如果存储的数据为“1”,cell存储节点N0是低电压,N1是高电压。因为DR1没有打开,另一条bit line BB保持平衡时的电压,而BT的电压值则会减小ΔVS 。

通过打开Column-select line for read(YSR)信号,由bit line构成的差分信号传输到灵敏放大器(sense amplifier)的输入端(ST/SB),经放大后又由output FF锁存输出。如果存储的数据为“0”,与此相似,只不过将会是bit line BB的电压减少。

执行写操作,同样也需要打开word line,在打开word line之前,将bit line电压平衡到VDD,由数据输入端过来的输入数据Din经由write amplifier(WA)传输至bit line。不同于读操作的是此时column 的选择由column-select signal for write (YSW)来控制。

Bit line电压变化后,使存储节点(N1,N2)的电压翻转,从而写入数据。最后,写操作完成时word line关闭。

Electrical Stability at Read Operation:Static Noise Margin and β Ratio

在正常读取数据模式下,假设node N0处于低电平,node N1处于高电平,字线被激活后,读电流(read current)由BT至N0流动,因此N0的电压会上升ΔVN(图2.4)。

不正常读取操作时,ΔVN大于DR1的阈值电压(Vth),DR1打开随之N1的电压减小,又导致N0的电压增大,最后致使cell翻转。

因此我们需要通过设计来避免出现不正常的读操作,其中一个重要的衡量稳定性的参数便是静态噪声裕量(SNM)。SNM参数表征了在读操作期间,cell 出现翻转的电压裕量。为评估SNM,将word line 和一对bit line连接到VDD(图2.5)。

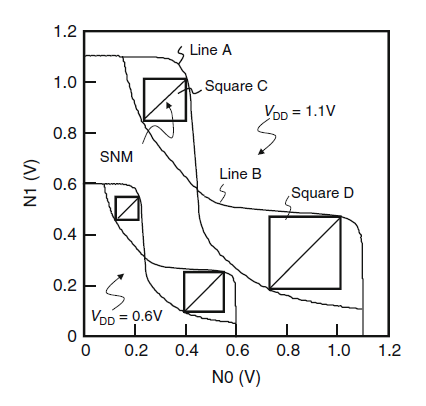

按如下方式进行仿真分析:

1.N0的电压由0V增加到VDD,同时测量N1的电压,绘制N1-N0的关系;

2.N1的电压由0V增加到VDD,同时测量N0的电压,绘制N0-N1的关系;

3.在曲线A和曲线B(或曲线C和D)中画出最大正方形。方形中较小那个的对角线就是SNM。

Fig. 2.5 Connections of the word line and a pair of bit lines to estimate the SNM

如图2.6所示,曲线A和曲线B被称作蝶形曲线“butterfly curb”,图中列出了VDD=0.6V和1.1V的情况,SRAM的工作电压越低,静态噪声裕量SNM越小。

蝶形曲线的不对称性受存储单元MOS管的阈值电压(Vth)变动影响,变化(variation)增加不对称性增加,导致SNM减小。

Driver MOSFET的阈值电压(Vth)较低,会减小SNM。Driver MOS和access MOS的栅宽之比称作比例因子β。通过增加driver MOS的电流,减小access MOS的电流,从而限制了N0电压的上升值ΔVN ,因此β增大,SNM增大。一般情况下,SRAM cell中,比率β大于1.5。

Fig. 2.6 Butterfly curbs are shown at VDD 0.6V and 1.1V

因为full CMOS 6-T memory 能在静态工作状态下保存数据,不需要额外的动态刷新。在读的时候,因为有电压相反的bit line信号配合输出给差分放大器,能在较短时间内获取数据。因此,SRAM在cache memory,mobile phone等等都都有应用,但SRAM cell 也需要在standby mode 下降低其保持数据所产生的功耗。