SystemVerilog中语法基本类型的简单介绍

数据类型中四值&二值逻辑的区分

verilog中数据类型均为四值逻辑,包括变量类型(variables)和线网类型(nets)。

-

variables类型包括例如reg、integer和time等,用来存储组合或者时序逻辑的值;

-

nets类型包括例如wire、wor和wand等,主要用于生成连线实现模块间连接以及提供特殊的线网逻辑解决方案等。

SystemVerilog将数据类型分为四值逻辑(logic)和二值逻辑(bit)。

- 四值逻辑硬件信号中变量或者线网类型,统一可以用logic声明。logic默认为变量类型(variable),也可以显示声明为线网型(nets);

- 二值数据类型,用来对于比RTL更高抽象级的模型建模,这些模型中Z和X很少被使用。包括,bit(1-bit)/byte(8-bit)/shortint(16-bit)/int(32-bit)/longint(64-bit)。

自定义类型

SV中通过自定义类型使得代码自身的可读性更好,也使得用户可以构建更高抽象层的数据类型。常见的包括:

- typedef,创建用户自定义类型;

- enum,创建枚举类型,描述变量的合法值范围;

- struct,创建结构体类型。

typedef又可以对enum,struct实现自定义枚举或结构体类型。

字符串类型

SV引入了string类型来容纳可变长度的字符串,同时包括一些字符串内建的方法,例如返回字符串长度str.len(),返回地i个字符串str.getc(i)等等。

SV字符串类型有以下特点:

- 存储单元为byte类型;

- 不同于c函数,没有空字符,长度为N,则索引为0~N-1;

- 内存是动态分配的

接口(interface)

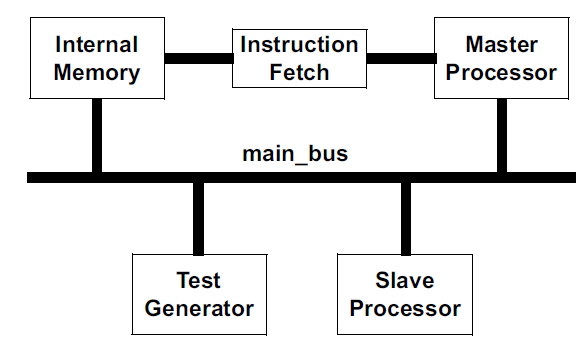

verilog中模块之间的通信需要例化端口和连线来完成,大型的设计中大量的端口让设计冗长和容易出错。因此,SV在Verilog基础上扩展了接口(interface)。

接口提供了一种新型的对抽象级建模的方式,可以使简化建模和验证大型设计。

优势:

- 允许多个信号被整合到一起表示一个单一的抽象端口;

- 多个模块可以使用同一个interface,避免分散的多个端口信号连接;

- 验证中,利用接口可以将测试平台同DUT连接在一起。

接口不同于模块(module)的地方在于,接口不允许包含设计层次,即接口无法例化module,但可以例化接口。进一步的,可以通过modport来约束不同模块连接时的信号方向。

小结:

- 接口有利于设计复用,减少了模块之间错误连接的可能性;

- 如需添加新的信号,可直接在接口中声明。因此,使用信号时需要添加一个层次(接口实例名);

- 接口一般将相关的信号集合在一起,设计中会包含多各接口实例。

Reference:

1.路科验证V0系列课程,可参考《芯片验证漫游指南:从理论到UVM的验证全视界》