什么是静态时序分析?

静态时序分析是一种不使用动态仿真,来检查电路是否满足时序约束的分析方法。

- Much faster than timing-driven,gate-level simulation

- Proper circuit functionality is not checked

- Vector generation NOT required

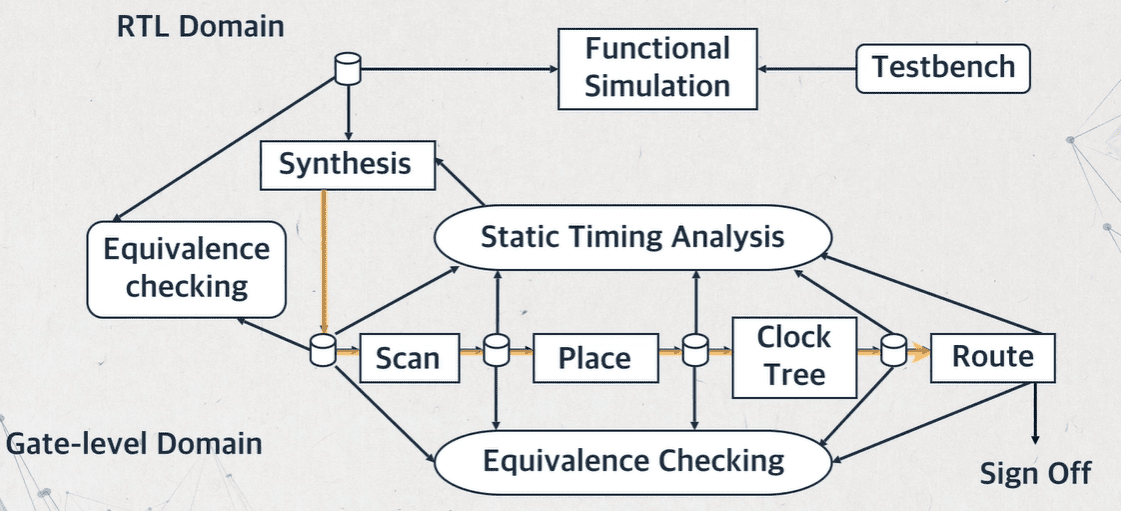

STA Flow

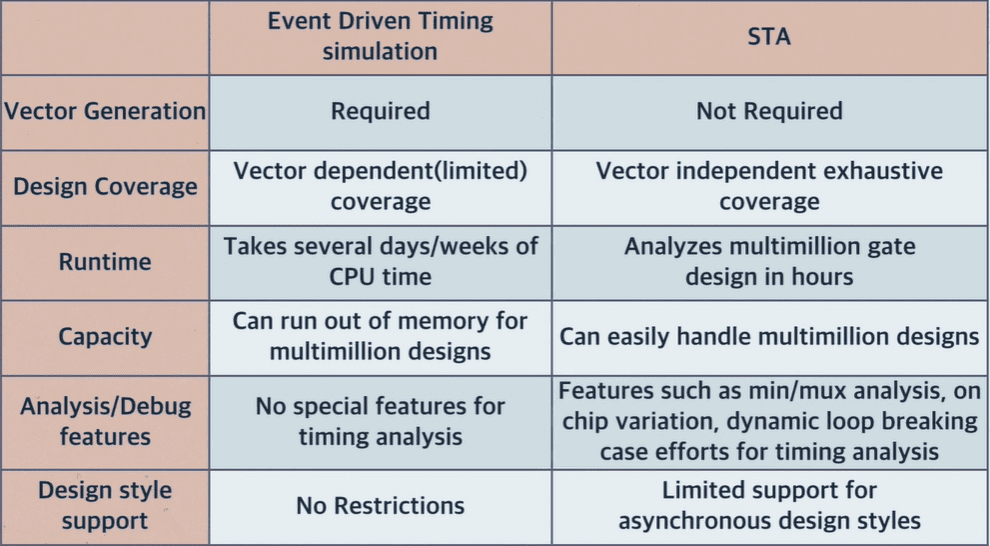

STA VS Event Simulation(互补)

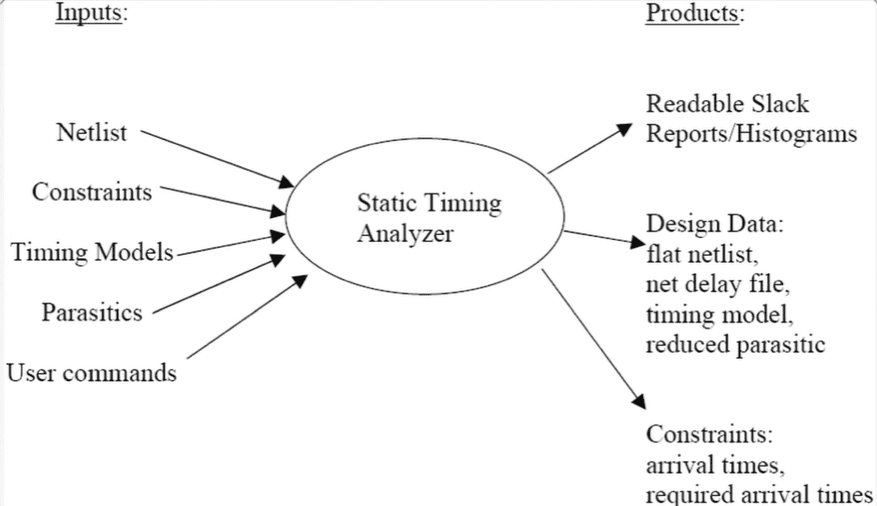

How STA Work?

Three Steps in Static Timing Analysis

1.Design is broken down into sets of timing paths;

2.Delay of each path is calculated;

3.Path delays are checked to see if timing constraints have been met

需要准备的文件和分析结果:

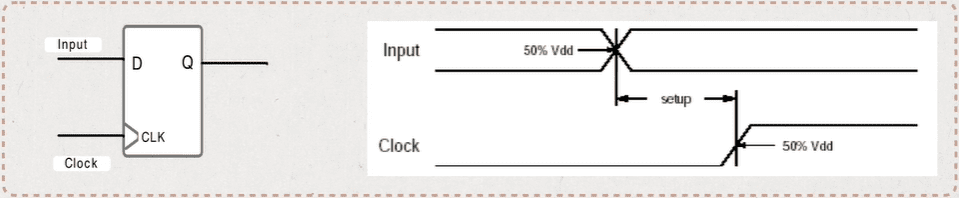

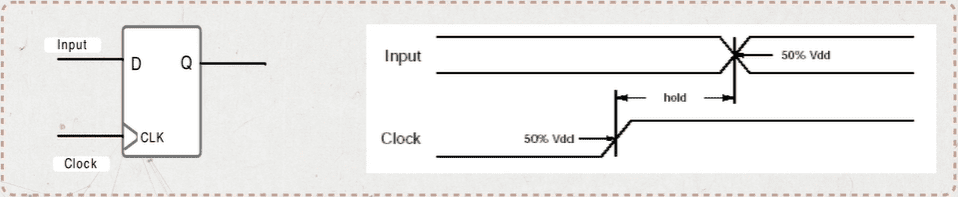

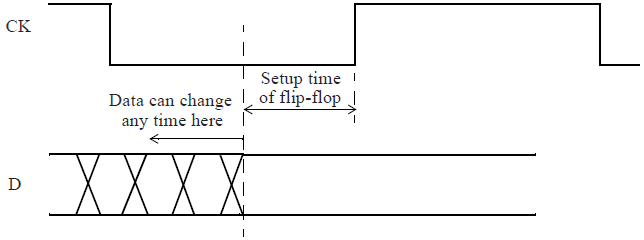

Setup Time-时钟边沿到来之前数据必须保持稳定的时间长度。

Hold Time-时钟边沿到来之后,输入引脚的输入数据依然要保持稳定的时间长度。

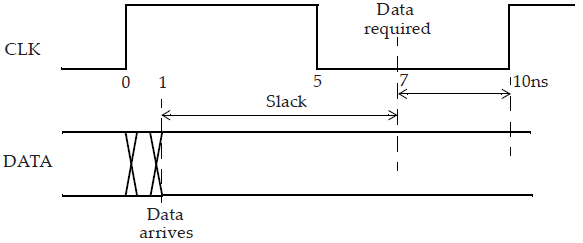

Time Slack

Slack is the difference between the required time and the time that a signal arrives.

- Positive slack or zero means meet constraints

- Negative slack means violate constraint

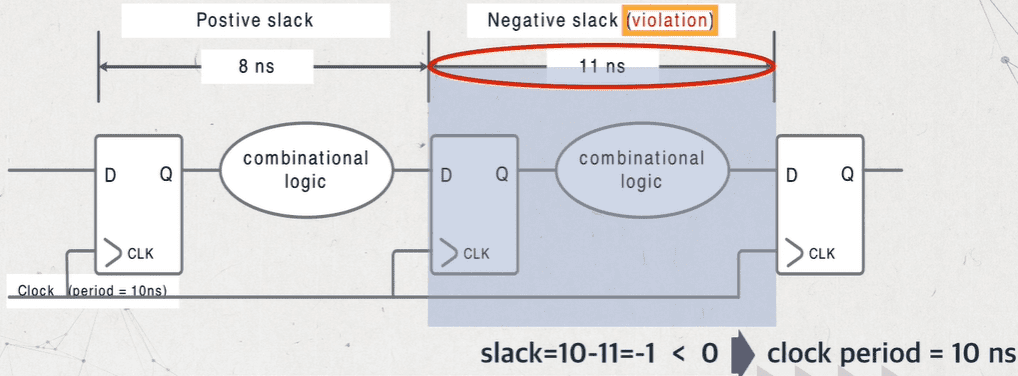

Speed VS. slack

- 整个同步电路系统的最大工作频率(minimum clock period)由最差逻辑路径所决定

- Slack 与时钟频率是息息相关的,例如clock period = 10 ns

Power VS. slack

如果 positive slack 较大,可以进步减小slack,使其保持为一个大于0的值。进一步缩小功耗和设计尺寸。

静态时序分析相比于逻辑综合时的时序分析区别在于,静态时序分析可以在逻辑综合、布局布线、时钟树综合每个阶段都可以进行的,越靠后延时信息分析越准确。

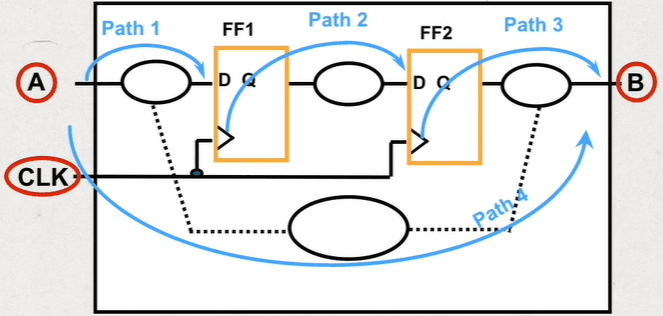

There are 4 Types of PrimeTime paths:

Input port to data pin of flip-flop(Path 1)

Clock pin of flip-flop to data pin of flip-flop (Path 2)

Clock pin of flip-flop to output port (Path 3)

Input port to output port (Path 4)

建立时间的检查(setup check)

A setup timing check verifies the timing relationship between the clock and the data pin of a flip-flop so that the setup requirement is met.

换句话说,建立时间的检查可以确保在flip-flop时钟有效沿到来时 ,数据到达flip-flop输入引脚时刻是稳定的。

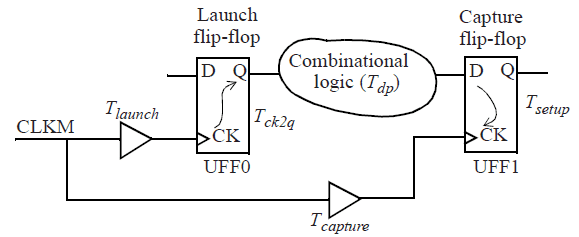

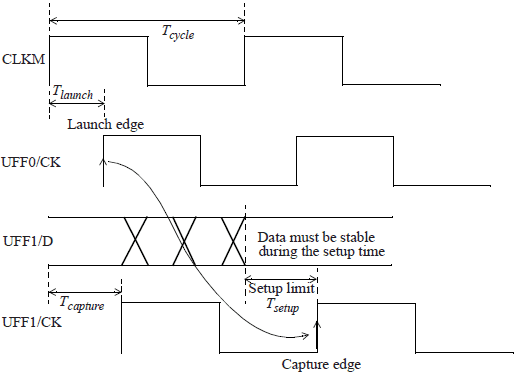

下面举一个简单的例子,如图所示,Launch & capture flip-flop使用的是同一个时钟CLKM。

第一个时钟上升沿,CLKM 经Tlaunch延时到达launch flip-flop UFF0,通过该时钟沿在时刻Tlaunch + Tck2q + Tdp数据被建立。

第二个时钟沿(setup is normally checked after one cycle)在时刻Tcycle + Tcapture到达capture flip-flop UFF1。

以上两条路径之间的时间差别需要满足大于flip-flop的setup time,这样才能使得数据稳定的捕获到flip-flop中。

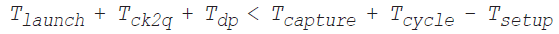

The setup check can be mathematically expressed as:

Tlaunch is the delay of the clock tree of the launch flip-flop UFF0;

Tdp is the delay of the combinational logic data path;

Tcycle is the clock period;

Tcapture is the delay of the clock tree for the capture flip-flop UFF1.

“ Since the setup check poses a max constraint, the setup check always uses the longest or the max timing path. For the same reason, this check is normally verified at the slow corner where the delays are the largest.”

Reference:

1.Static Timing Analysis for Nanometer Designs A Practical Approach