减少设计面积,意味着成本降低、功耗降低。特别是对于FPGA的设计,直接决定着FPGA的选型。

为了减少设计面积,首先得估算设计使用资源的数量,例如触发器、加法器、乘法器等。其中,触发器的数量由功能决定,很难减少,其面积也比较好估计。因此,RTL设计中的组合逻辑,对应的各种操作符在使用的时候应该加以重视。例如,加减法、乘除法以及条件语句中的比较运算。

RTL编码中考虑面积

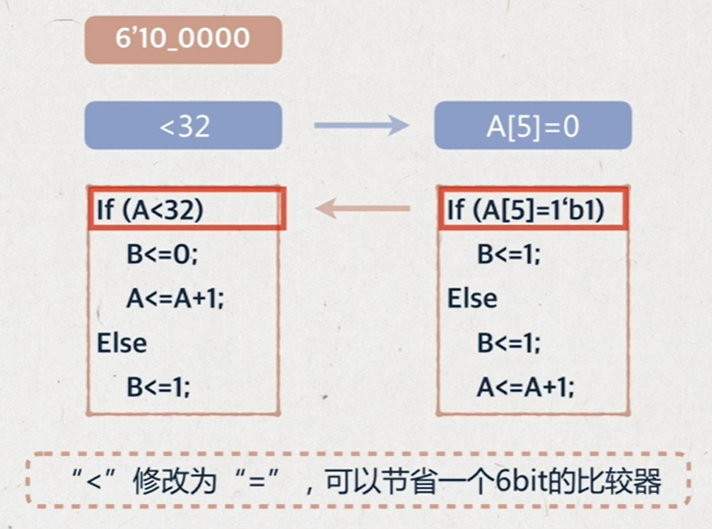

如以下实例中,替换判断语句后,实现了1bit逻辑门省掉了一个6bit的比较器。

对于一些定值的数据,类似操作都可以如此考虑RTL设计来节省面积。

如果,必须使用复杂的运算符,则应考虑是否可以资源共享。尽管电路逻辑综合工具也会在综合的过程中采用资源共享的方法进行优化,但是,综合器的策略是有限的,因此,在编写RTL的时候,应该尽量考虑共享,而不是把这项工作完全留给综合工具。

例如:

1 | if(y1>a+b+q) |

可以将a+b的值sum进行资源共享修改为以下所示,减少了两个不必要的加法器。

1 | sum<=a+b; |

除了操作符以外,我们仍需注意多比特数据的使用,其会占用乘倍的资源,应该分析信号的所有比特位是否都需要参与操作,如果不是,咋可以只对需要的部分进行操作。

例如:实现加32的操作

addr <= addr + 32; 更换为 { addr[7:5] <= addr[7:5] + 1; addr[4:0] <= addr[4:0] + 0}

RTL编码中考虑功耗

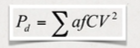

动态功耗的计算公式可以表述为:

在RTL设计,负载电容和工作电压是无法改变的,主要尽量降低电路的反转频率。

主要措施:

(1)门控时钟,门控时钟是电路设计最常用也是最有效的方法,在逻辑综合阶段可以让综合工具自行插入。

(2)增加使能信号,使得部分电路只有在需要工作时才工作;

(3)对芯片各个模块进行控制,在需要工作时才工作;

(4)除了有用信号和时钟的翻转会消耗功耗,组合逻辑产生的毛刺也会大量消耗功耗。但是,毛刺在设计中无法避免,因此,只有尽量减少毛刺在电路中的传播,才可以减少功耗。即,在设计中,尽量把产生毛刺的电路放在传播路径的最后。另外,可以使用一些减少毛刺的技术。

(5)对于有限状态机,可以通过低功耗编码来减少电路的翻转。

总的来说,使用这些技术时,应首先考虑全局的功耗控制。

然后再RTL编码中,注意消耗功率较多的电路,如状态机、译码器、多路选择器等。

最后,在综合中,使用门控时钟和其他减少功耗的优化技术。

这里要注意下门控时钟和增加使能控制的区别。增加使能仅仅是使得电路的信号不在翻转,但是时钟每个周期还会继续翻转。而门控时钟则是直接关掉时钟,这种方法效果更好。

RTL中考虑布线问题

布线(routing),旨在根据门级网表的描述实现各个单元的连接。布线是否能够顺利布通的最关键因素是布局(placement)。但是,即使最好的布局工具,还是可能出现无法布通的情况。这种情况下就需要修改RTL级设计。

因此,如果可以在RTL编码 阶段考虑代码可能对布线产生的影响,就可能避免最后出现无法布通的情况。

热点:指设计中的功能需要在一个面积内占用大量的布线资源

热点产生的原因,主要是RTL编码时使用了特定的结构,如很大的MUX。如果设计中的却是需要采用较大的MUX,可将MUX分级为多级较小的MUX。

参考:芯动力—硬件加速设计方法