CMOS反相器的性能:动态特性

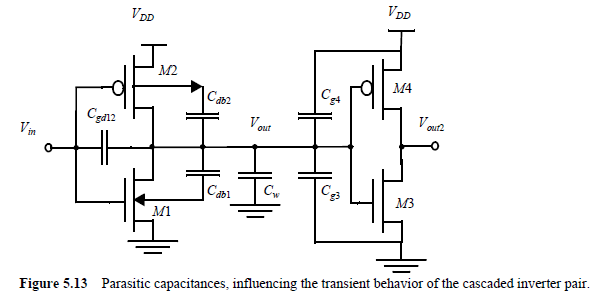

CMOS反相器的传播延时取决于它分别通过PMOS和NMOS管充放电负载电容CL所需要的时间。使CL尽可能小是实现高性能CMOS电路的关键。

电容值分类

- 栅漏电容Cgd12

- 扩散电容Cdb1和Cdb2

- 连线电容CW

- 扇出的栅电容Cg3和Cg4

传播延时:一阶分析

等效导通电阻Req,反相器的总传播延时:tp = (tpHL + tpLH)/2,其中:

tpHL= 0.69 ReqnCL

tpLH= 0.69 ReqpCL

减小门传播延时:

-

减小CL:负载电容由三个主要部分组成:内部的扩散电容、互连线电容和扇出电容。通过细致的版图设计有助于减少扩散电容和互连线电容

-

增加晶体管的W/L比:可以减小等效电阻,是最有力和最有效的性能优化工具。

同时增加晶体管尺寸也会增加扩散电容,因而增加CL,当本征电容超过由连线和扇出行成的外部负载时,增加门的尺寸不再对减少延时有帮助。

较宽的晶体管具有较大的栅电容,增加了驱动门的扇出系数,从而反过来影响它的速度。 -

提高VDD:牺牲功耗来换取性能

从设计角度考虑传播延时

NMOS和PMOS的比

通常要求PMOS与NMOS的宽度比在3~3.5之间,使得设计反相器具有对称的VTC,并使得tpHL =tpLH。但如果对称性和噪声容限不是主要的考虑因素,可通过减小PMOS器件的宽度来加快反相器的速度。原因是,是PMOS较宽可以改善反相器的tpLH ,但它也由于产生较大的寄生电通而使tpHL 变差。

考虑性能时反相器的尺寸的确定

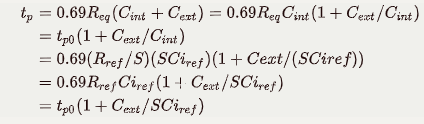

负载电容划分为:CL = Cint + Cext,其中 Cint 即本征输出电容, Cext是外部负载电容,来自扇出和导线电容。

Leads two important conclusions:

- 反相器的本征延时tp0与门的尺寸无关,而只取决于工艺及方相器的版图;

- 使S无穷大将达到最大可能的性能改善,使延时减小到只有本征延时值。

确定反相器链的尺寸

每一个反相器的最优尺寸是与它相邻的前后两个反相器尺寸的几何平均数,即每个反相器都具有相同的等效扇出,也就具有相同的延时。可以推导出尺寸系数f。

选择一个反相器链的正确级数

简化条件下可以得到最优的级数为N = ln(F)。

选择的扇出值大于最优值并不会过多的影响延时,但能减少所要求的缓冲器级数和实现面积。

输入信号的上升-下降时间

保持门的输入信号的上升时间小于或等于门的传播延时是很有利的。

存在(长)互连线时的延时

当门之间的距离进一步加大之后,互连线的电容和电阻就不容忽略,也使得导线延时在较长导线的总延时中总迅速占据主要地位。(延时表达式中有一个与导线长度呈线性关系和一个成平方关系的部分)

功耗、能量和能量延时

动态功耗

反相器门开关过程中,由充放电电容引起的功耗

设计技术

改变器件尺寸并降低电源电压是减小一个逻辑电路能耗的非常有效的方法;

在最优值之外过多地加大晶体管尺寸会付出较大的能量代价。至今许多设计仍普采用这种方法;

考虑能量时的最优尺寸系数小于考虑性能时的最优尺寸系数

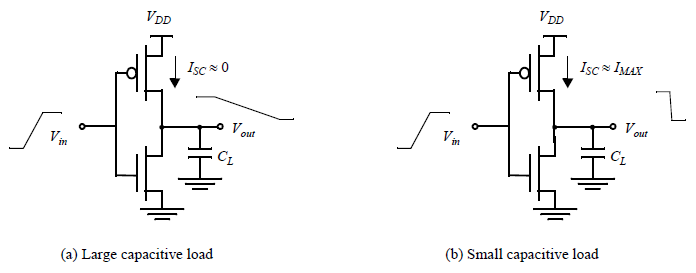

直通功耗

由于输入波形的上升和下降时间为零。开关过程中VDD和GND之间在短期内出现一条直流通路,此时NMOS和PMOS同时导通。直接通路电流引起功耗

设计技术

使输出的上升/下降时间大于输入的上升/下降时间可以使短路功耗减到最小;

从全局的角度看,应该使所有信号的上升/下降时间保持在一定范围内不变。当负载电容太小时,功耗主要来自于短路电流,对于非常大的负载电容值,功耗主要是电容充电和放电产生。

静态功耗

由于泄漏电流流过位于晶体管源(或漏)与衬底之间的反相偏置的二极管结而形成的静态功耗;晶体管的亚阈值电流。

设计技术

阈值电压的选择代表了在性能和静态功耗之间的权衡取舍。降低电源电压而保持阈值电压不变会造成性能的严重损失,阈值电压的最低值又是由所允许的亚阈值漏电电流的数量所决定的。

通过权衡选择正确的电源值和阈值电压值;

当存在较大静态功耗时,使不工作的模块暂时断电以减少静态功耗。

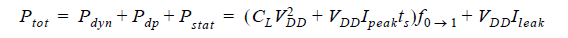

综合考虑

CMOS反相器的总功耗可以分为三部分的和:

其中Pdyn为电容功耗,Pdp为直接通路功耗,Pstat为漏电功耗。

功耗—延时积或每次操作的能量损耗

衡量了开关门所需要的能量

能量—延时积

衡量电源电压(即性能)与延时之间的矛盾关系

小结

- 静态CMOS反相器,组合了一个上拉PMOS和一个下拉的NMOS,由于PMOS有较低的电流驱动能力,通常使它比NMOS宽。

- 理想的电压传输特性。逻辑摆幅等于电源电压并且与晶体管尺寸无关。噪声容限接近VDD/2.稳态响应不受扇出的影响。

- 传播延时主要由充放电负载电容CL所需要的时间决定。一阶近似为,tp=0.69CL((Reqn + Reqp)/2),使负载电容较小是实现高性能电路的最有效手段。

- 功耗主要由充放电负载电容时消耗的动态功耗决定。功耗与电路的活动性成正比。开关通断期间的直接通路功耗可以通过对信号斜率的仔细修正来限制。静态功耗通常可以忽略,但由于阈值电流的原因可能成为一个主要因素。

- 工艺尺寸变小是减少一个门的面积、传播延时以及功耗的有效手段。同时降低电源电压,影响更大。

- 互连线的影响将在总延时和总性能中逐渐占有更大的比例。

参考资料:

Rabaey J M, Chandrakasan A P, Nikolić B. Digital integrated circuits: a design perspective[M]. Upper Saddle River, NJ: Pearson Education, 2003.