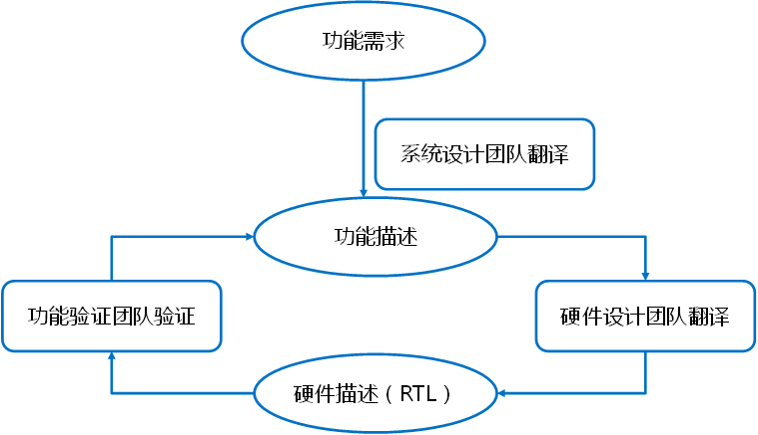

芯片验证为IC设计流程中前端设计的重要一环,用其来证明设计功能是否正确,是否符合设计功能描述。

验证和设计是协作进行的,验证和设计都需要认真阅读功能描述文档。设计将功能文档翻译为RTL模型,验证则会按照其功能发送激励和比较结果。

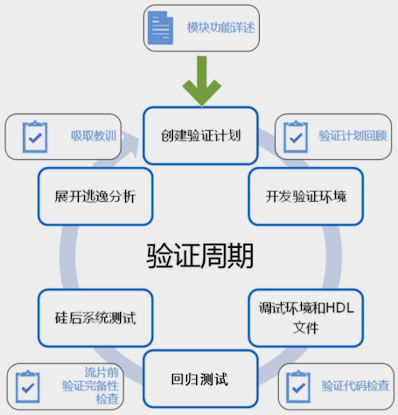

验证的周期

功能验证有着一整套完备的流程,从硬件系统定义贯穿到硅后测试部分。

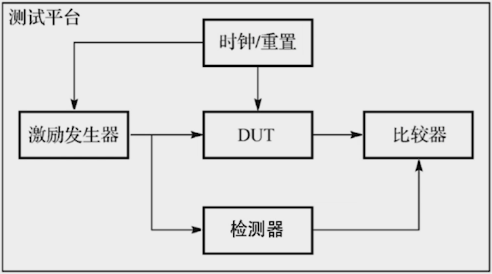

什么是验证测试平台?

如图所示,测试平台主要包括的模块有时钟/重置(clock/reset)、激励发生器(stimulator)、检测器(monitor)、比较器(checker)以及待测设计(DUT)。其中:

- Stimulator:对DUT创建测试序列

- Monitor:观察DUT的输入输出

- Checker:对DUT的输出数据与预期数据进行比对

除此以外,clock/reset完成时钟的发起以及复位工作。最终,测试平台还会报告检查结果。

什么是SystemVerilog?

SystemVerilog是一种新的硬件描述和验证语言(HDVL, Hardware Description and Verification Language)。

SV语言的核心特性

- 接口(interface)

- 面向对象编程(class&package)

- 约束随机(constrained random)

- 线程控制和通信(process control)

- 功能覆盖率(function coverage)

- 外部语言编程接口(Direct Programming Interface)

- 断言(assertion)

什么是UVM?

UVM(Universal Verification Methodology),是一种可适用于大多数项目的验证方法学。它自身提供的基础类库和验证结构可以让具有不同软件编程经验的验证工程师能够快速构建起一个可靠的验证框架;其框架构建类和测试类能够减轻环境构建的负担,进而将精力集中在如何制定验证计划和创建测试场景上。

学习UVM时,可以遵循以下步骤:

- 认识UVM世界的版图(类库)和核心机制

- 学习核心的UVM组件和层次构建方式

- 了解常见的UVM组件间的通信方式

- 深入UVM测试场景的构成

- UVM的寄存器模型应用

UVM的类大致包括以下几类:

- 核心基类

- 工厂(factory)类

- 事务(transaction)和序列(sequence)类

- 结构创建(structure creation)类

- 环境组件(environment component)类

- 通信管道(channel)类

- 信息报告(message report)类

- 寄存器模型(register model)类

- 线程同步(thread synchronization)类

- 事务接口(transaction interface)类

Reference:

1.路科验证V0系列课程,可参考《芯片验证漫游指南:从理论到UVM的验证全视界》