状态机的本质是对具有逻辑顺序或时序规律事件的一种描述方法。

状态机的基本概念

应用思路:

-

从状态变量入手

根据电路的时序规律或者逻辑顺序,规划状态,分析状态的输入、转移及输出

-

明确电路的输出关系,这些输出对应于状态的输出,进而回溯规划每个状态和状态转移条件及输入

基本要素:状态、输出、输入

描述方式:状态转移图、状态转移列表、HDL语言描述

常见分类:

-

摩尔型状态机,输出仅依赖于当前状态,而与输入条件无关

-

米勒型状态机,输出不仅依赖于当前状态,而且取决于该状态的输入条件

-

根据状态机的数量是否为有限个,可分为有限状态机(Finite State Machine,FSM)和无限型状态机(Infinite State Machine,ISM)

如何写好状态机

好的RTL级FSM描述具备以下特点:

- FSM要安全,稳定性高;

- FSM速度快,满足设计的频率要求;

- FSM面积小,满足设计的面积要求;

- FSM要清晰易懂、易于维护

即在FSM中需要注意完备性,综合的结果无毛刺等异常扰动,在满足时序要求的前提下,占用最小的面积,或者在满足面积要求的情况下,是设计的时序余量更大,频率更高。

一段式状态机

应该避免的写法。

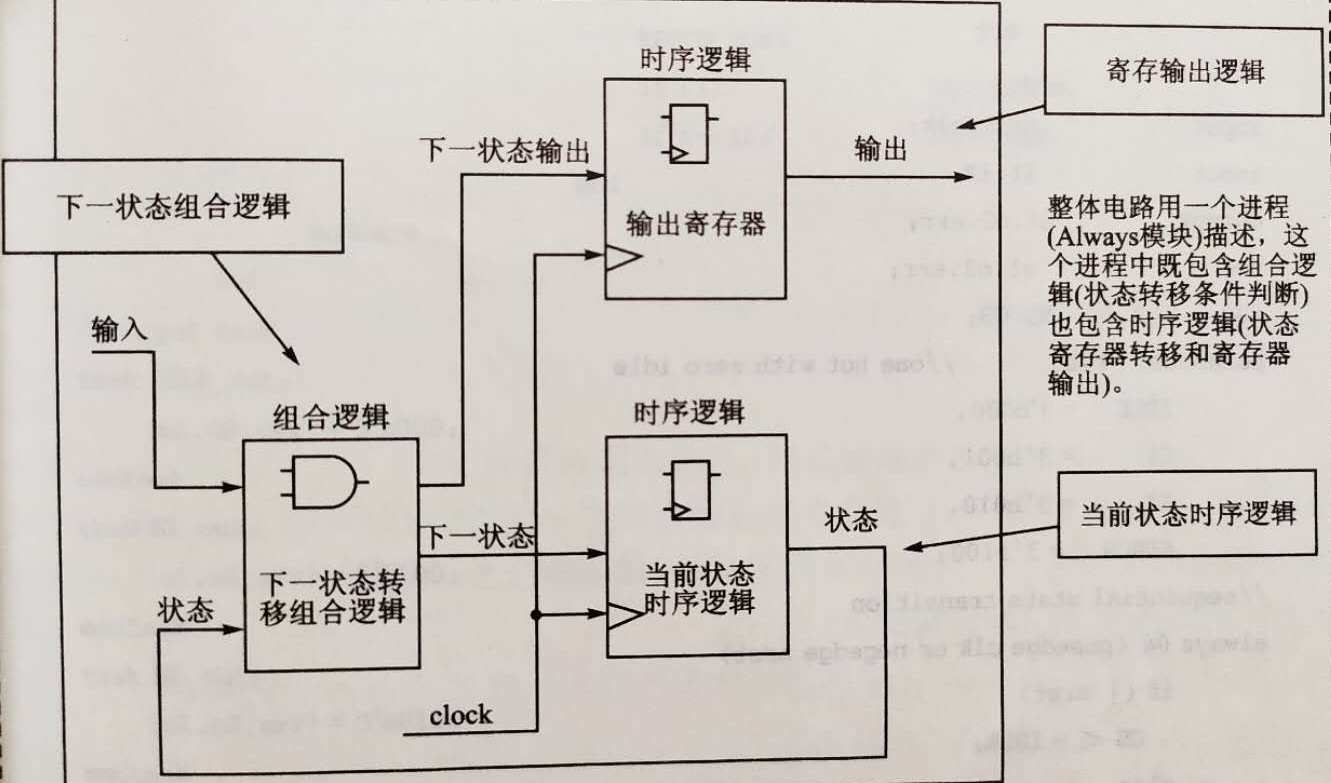

设计的整个状态机写到1各always模块中,在该模块既描述状态转移,又描述状态的输入输出,这种写法称为一段式。

主要缺点:

- 状态转移判断的组合逻辑和状态寄存器转移的时序逻辑混写在同一always模块中,不符合时序和组合逻辑分开描述的coding style;

- 代码结构不清晰,不利于维护,且不利于附加约束,不利于综合器和布局布线对设计的优化;

- 另外该描述方法冗长,一般来说,一段式代码长度会比两段式长大约80%~150%。

两段式状态机

推荐的FSM描述方法之一。

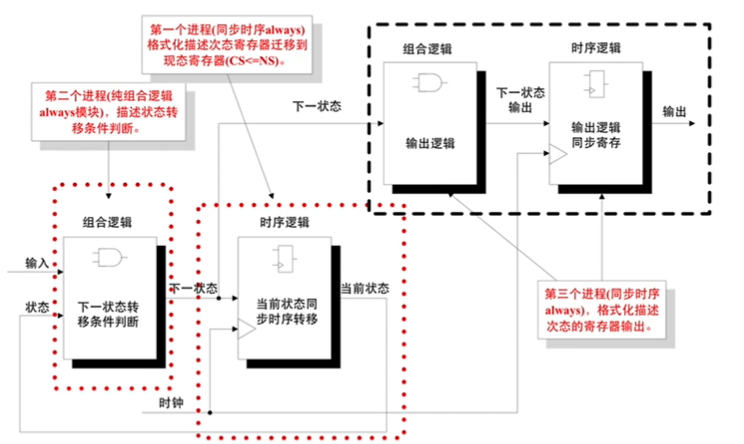

实现方法,一个always模块采用同步时序描述状态转移;另一个模块采用组合逻辑判断状态转移条件,描述状态转移规律。

缺点:输出一般使用组合逻辑描述,容易产生毛刺等不稳定因素。

三段式状态机

比较推荐的写法。

关键在于使用同步时序逻辑寄存FSM的输出。

两段式状态机根据CS 决定输出结果,而三段式状态机根据NS 决定输出结果

优势:

-

使FSM做到了同步逻辑;

-

消除了组合逻辑输出的不稳定与毛刺的隐患;

-

更利于时序路径分组;

-

在FPGA/CPLD等可编程逻辑器件上的综合与布局布线效果更佳

RTL

两段式状态机

1 | //Add a default state to make it more safe |

三段式状态机

1 | //3-paragraph method to describe FSM |

Reference:

1.轻松成为设计高手–Verilog HDL 实用精讲