快时钟域向慢时钟域过渡时如何采用“结绳法”进行过渡以及多bit指示信号和多bit数据流的跨时钟域处理方法

结绳法(快时钟–>慢时钟)

信号从快时钟域到慢时钟域过渡时,慢时钟将可能无法对变化太快的信号实现正确采样,前述同步器对两个时钟之间的关系要求很严格,采用“结绳法”则适合任何时钟的过渡。

原理:

- 将时钟信号的脉冲周期延长,等到慢时钟同步采样后再“解绳”,还原为原来的脉冲周期宽度。

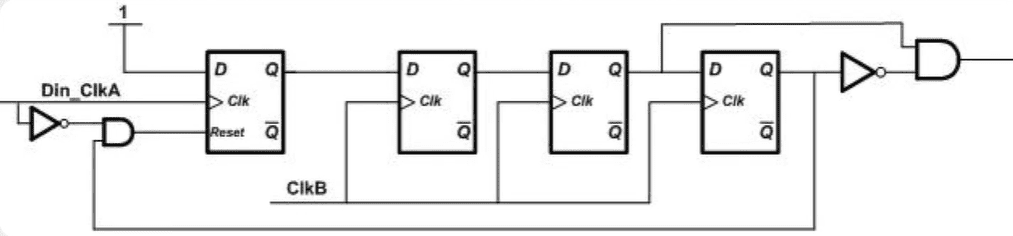

结绳法1:

利用数据的边沿作时钟(图中上升沿)。数据作为Din_ClkA,当有数据有上升沿(0–>1)时,寄存器1稳定在高电平。等待CLKB采样,采样后寄存器4输出高电平,若此时Din_ClkA为低电平,即完成复位,开始下一次采样等待。

注意:

数据来临时,CLKB需要等待3个周期,最终通过寄存器4反馈数据信息完成复位。如果Din_CLKA变化较快,即持续时间短于3个CLKB,也就是频率大于1/3 CLKB,此时Din_CLKA的变化将无法被采样到,因为CLKB域需要3个CLKB周期才能完成采样,并且此时DIN_CLKA必须是低电平才能复位,采用异步复位。

在慢时钟采样快时钟的时候,结绳法适合采样数据较少(即脉冲间隔较大)的控制信号。即脉冲间隔Ta > 3Tb;即等待3个CLKB时钟后,完成复位,才允许下一个输入脉冲。

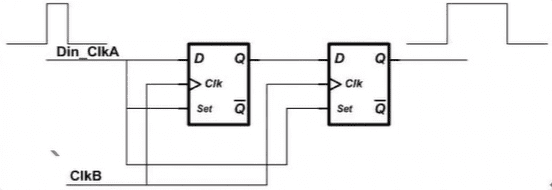

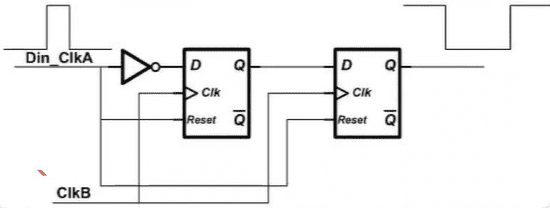

结绳法2:

利用数据作为异步复位,置位信号。

结绳法3:

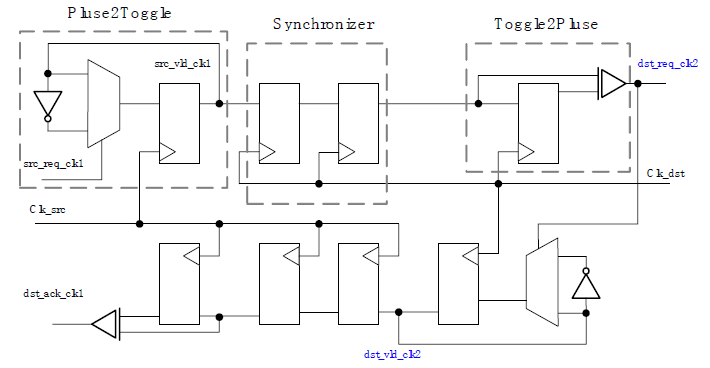

利用握手协议

下图描述了实现方法,主要包括三个基本单元:Pluse2Toggle, Synchronizer 和Toggle2Pluse:

- Pluse2Toggle模块负责将两个脉冲信号“结绳”,即将单脉冲信号延长;

- Synchronizer模块即用双锁存器法将得到的信号过渡到另一个时钟域;

- Toggle2Pluse模块是Pluse2Toggle功能相对,即将延长的脉冲信号还原为单脉冲,这里用到了异或门

整体的设计思想即用Pluse2Toggle将信号延长,用Synchronizer过渡,用Toggle2Pluse还原,以保证另一个时钟域可以正确采到,而接收方用相反的流程送回响应信号。

“结绳法”波形示意图如下所示。

在两次src_req_clk1之间被src_vld_clk1“结绳”(pluse2toggle),在将src_vld_clk1用双锁存器同步以后,将该信号转换为dst_req_clk2(toggle2pluse)。同理,用dst_vld_clk2将dst_req_clk2“结绳”,dst_vld_clk2表明在clk2时钟域中,src_dat_clk1已经可以进行正确采样了。最后将dst_vld_clk2转换为dst_ack_clk1(synchronizer and toggle2pluse), dst_ack_clk1表明src_dat_clk1已经被clk2正确采样了, 此后clk1时钟域就可以安全地传输下一个数据了。可以看出,“结绳法”关键是将信号结绳以后,使其保持了足够长的时间,以便另一个时钟可以正确地采样。

小结:

-

结绳就是将单脉冲延长,以方便采集到的数据;

-

方法可归结为2类,利用脉冲的边沿做时钟;利用脉冲的电平(部分场合要求最小脉冲宽度)做选择器或者异步复位;

-

关键点在于是什么时候结绳结束;

-

操作方法有2种,利用采集到的脉冲做异步复位,置位;利用采集到的脉冲再次结绳采集做握手响应信号;

-

结绳法可以解决快时钟域向慢时钟域过渡的问题,且其适用范围很广;

-

结绳法实现较为复杂,特别是效率不高,在对设计性能要求较高的场合应该慎用。

考虑两个问题

-

采样中“快到慢”与“慢到快”在考虑问题时有什么区别?

慢到快,只需要考虑亚稳态问题;

快到慢,除亚稳态问题外,还需要考虑慢时钟的采样速率问题。。

-

为什么不能用慢时钟直接采样快时钟域的信号?

因为根据采样定理,采样频率低于信号最高频率2倍的时候,是无法完整采样的

多bit指示信号的跨时钟域传输

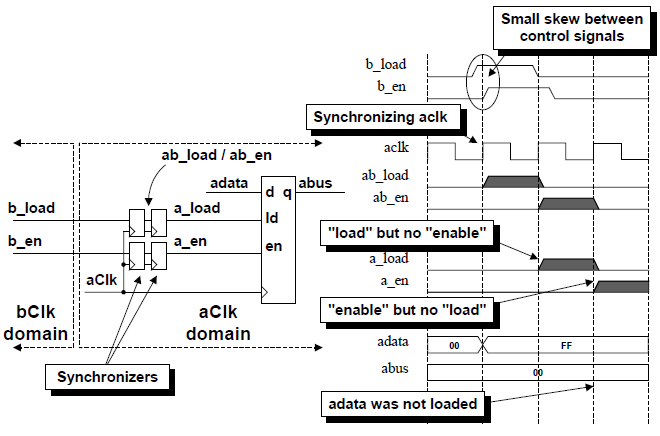

同时传递两个信号(b_load & b-en),如下图所示。

图中b_load 和b_en同步至a_clk时钟域,如果这两个信号有一个小的skew,将导致a_clk时钟域中两个信号并不是在同一个时刻起作用,与两个信号在b_clk时钟域中的逻辑关系不同。

多个控制信号跨时钟域仅仅通过简单的同步器同步有可能是不安全的

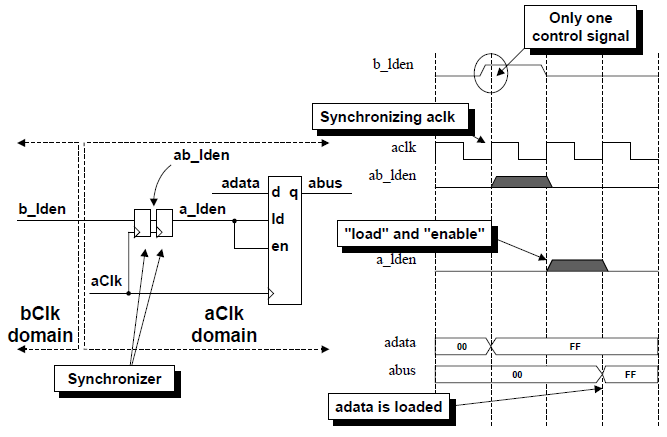

解决方法:将b_load和b_en信号在b_clk时钟域中合并成一个信号b_lden,然后同步至a_clk中

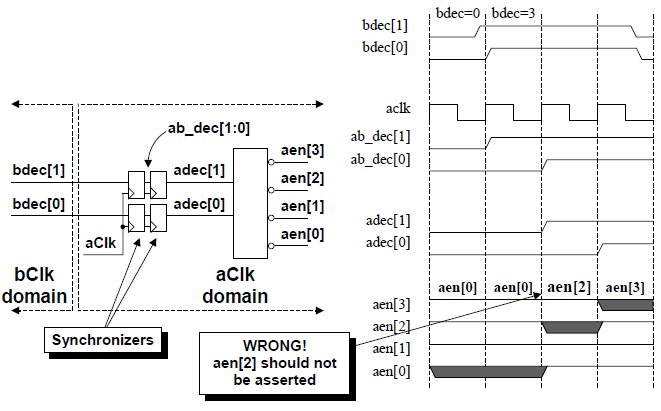

如果遇到不能同步的情况,如译码信号,如下图所示。

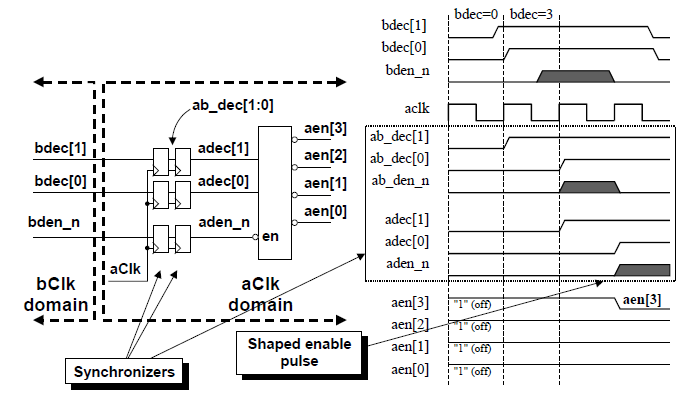

解决方法1:建议加入另一个控制信号,确保bdec[0]、bec[1]稳定时再进行采样。

解决方法2:在发送时钟域解码,通过同步器来同步发送时钟域的输出到新的时钟域。在新的时钟域内,使用状态机确定何时被同步的输入有效。

多bit数据流的跨时钟域传输

数据流和指示信号的区别:

- 数据流大多具有连续性,即背靠背传输;

- 数据流要求信号具有较快的传输速度

解决方法:SRAM、FIFO

FIFO基本介绍

FIFO(first in first out),是一种先进先出的存储结构。与普通存储器相比没有外部的读写地址线,使用简单。

缺点在于只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

**异步FIFO即用一种时钟写入数据,而用另外一种时钟读出数据,其中这两个读写时钟是异步的。**适用于大量数据跨时钟域传输,且对传输速度有一定要求的场合。

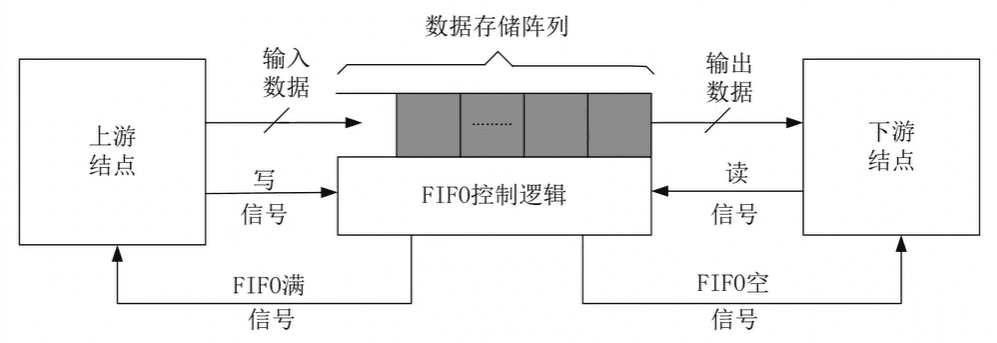

FIFO 上游节点是FIFO的数据输入端,在写信号有效时,数据将被写入FIFO的顶部(由FIFO内部的写指针控制),并且在FIFO内部,写指针后移一个单元,同时FIFO的满信号(FIFO full signal)将控制上游节点是否发送数据;

FIFO 下游节点是FIFO 的数据输出端,当读信号有效时,位于FIFO底部的数据将被读出(由FIFO内部的读指针控制),并且在FIFO内部读指针将后移一个单元,同时FIFO空信号(FIFO empty signal)将控制下游节点是否读出数据。

FIFO主要用途:

-

使用异步FIFO对不同时钟域之间的数据进行传输;

-

对于不同宽度的数据接口也可以用FIFO

例如单片机8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配目的。

Reference:

2.Synthesis and Scripting Techniques for Designing Multi-Asynchronous Clock Designs